ENGINEERING SERVICES HI-TECH

Stay connected

### **HARDWARE DESIGN**

#### HIGH BANDWIDTH FPGA PLATFORM

- Challenge High component density with restricted layer build.

- ♦ High speed PCle (8Gbps), FMC (12.5Gbps), SFP+ (10Gbps)

- Prequalified 1996 pin BGA device

- Shall address all DFx, issues to meet cost effective production

- Socket based design to integrate DDR3, RLDRAM3, and QDRII memory devices

#### **ENTERPRISE STORAGE**

- ◆ Redundant SAS 3 12G based 2U/3U base platform with capacities 100TB to 360TB

- Customized Board Management controller

- Redundant system power distribution of 1600W

- ~250 SAS 3 lanes with trace lengths more than 20 inches

## **ENTERPRISE HIGH CAPACITY/PERFORMANCE STORAGE**

- ♦ High capacity 2TB to 8TB, Flash based pluggable memory modules, with small form factor.

- High density Component placement (10 mil spacing between components)

- Compliant to JEDEC PCB form factor and board thickness, limiting the no of layers used while ensuring signal integrity.

- Propriety interposer PCB technique to double memory capacity

- Design optimized to minimize components to meet PCB form factor

## SATELLITE, TERRESTRIAL AND IP SET TOP BOXES

- Standard Definition Satellite STB

- Onboard Legacy TV interface output support

- Smart card Support, DC power input

- Low Cost solution and Mass manufactured

#### **Technology**

- HD, PVR Expertise; HDMI, SPDIF, RGB, SCART Expertise

- NAGRA, NDS support

- Mechanical Design ( Metal and Plastic)

- Video Decoder across vendors like ST Micro, Broadcom, NXP

- Exposure to cable, satellite, IP and terrestrial STB's

- DVT and Characterization

# **HARDWARE DESIGN**

### **MULTI BOARD SIGNAL INTEGRITY ANALYSIS**

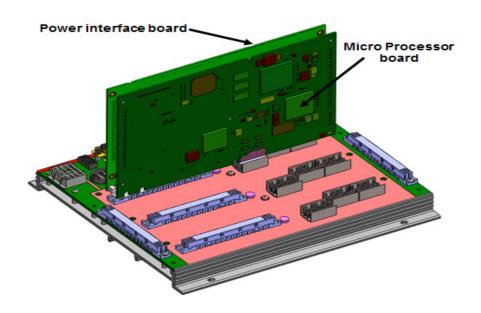

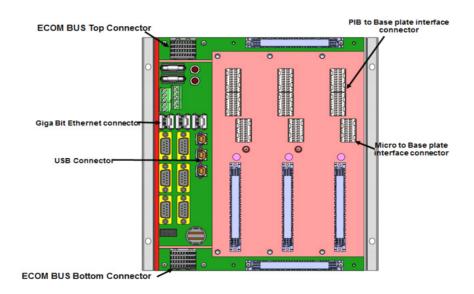

To analyze and recommend signal topologies and interconnect rules for high speed signals from a micro-processor controller board to redundant modules through a motherboard and board end connectors.